Analiza tipurilor

de memorie SRAM şi DRAM

1. Obiectivul lucrării

Lucrarea de

faţă îşi propune prezentarea comparativă a modulelor de memorie RAM statice (SRAM)

şi dinamice (DRAM) din punct de vedere al construcţiei,

funcţionării, parametrilor şi performanţelor.

2. Introducere teoretică

Subsistemul de memorie al unui calculator reprezintă ansamblul unităţilor de memorie, împreună cu algoritmii necesari pentru controlul transferurilor şi memorarea informaţiilor, algoritmi care pot fi implementaţi hardware sau software. Subsistemul de memorie include atât locaţiile de memorie propriu-zise, cât şi circuitele necesare pentru adresarea locaţiilor şi controlul operaţiilor de citire şi scriere. O parte din aceste circuite se găsesc în unitatea de memorie respectivă, altele sunt externe, fiind de obicei integrate în controlerul unităţii de memorie.

Obiectivul

principal în proiectarea oricărui subsistem de memorie este realizarea unei

capacităţi de memorare adecvată sistemului de calcul, cu un

nivel acceptabil de performanţe, la un cost rezonabil. Trebuie subliniat

faptul că nu întotdeauna obiectivul este acela de a obţine o

capacitate de memorare cât mai mare.

2.1. Caracteristicile unităţilor de memorie

Capacitatea de memorare reprezintă numărul

locaţiilor (celulelor) de memorie conţinute de o unitate de memorie.

Aceasta depinde de tehnologia de fabricaţie şi se exprimă în

cuvinte de informaţie memorată (cuv), dimensiunea cuvântului fiind

diferită de la un calculator la altul.

Timpul de acces la o unitate de memorie (tA) este timpul necesar

localizării unei celule de memorie, pentru transferul de informaţii

la/de la locaţia de memorie respectivă. Acesta reprezintă intervalul

de timp calculat din momentul în care o unitate master lansează o

comandă către o unitate de memorie şi până în momentul în

care informaţia este transferată în sensul dorit.

Rata de acces (rA) este inversa timpului de

acces, fiind exprimată în cuvinte pe secundă:

rA = ![]() [cuv/s]. (1)

[cuv/s]. (1)

Timpul de ciclu la o unitate de memorie (tC) este timpul minim între

două accese succesive şi reprezintă timpul din momentul în care

o unitate master lansează o comandă (COM 1) spre unitatea de memorie

şi până când poate lansa o nouă comandă (COM 2) la

aceeaşi unitate de memorie. tC > tA,

diferenţa lor numindu-se timp de

revenire (tR = tC

– tA). Acesta reprezintă timpul minim necesar

pentru inactivarea primei comenzi, până la activarea celei de-a doua.

Rata de transfer (rT) este inversa timpului de

ciclu şi reprezintă cantitatea maximă de informaţie

(exprimată în cuvinte pe secundă), care poate fi transferată

la/de la memorie într-o secundă:

rT = ![]() [cuv/s]. (2)

[cuv/s]. (2)

Costul total al unităţii de memorie (CT) include, pe lângă

costul celulelor de memorie propriu-zise, şi costul circuitelor de acces

la aceste celule. Pentru compararea diverselor unităţi de memorie

între ele, se utilizează costul

unitar (CU),

care reprezintă costul de memorare a unui cuvânt de informaţie.

Costul unitar se determină prin raportarea costului total (CT)

la capacitatea de memorare (CM):

CU = ![]() [cost/cuv]. (3)

[cost/cuv]. (3)

Cu cât memoria este mai

rapidă, cu atât costul unitar este mai mare.

Modul de acces la locaţiile unităţii de

memorie

arată ordinea în care informaţia memorată poate fi

accesată. Acesta poate fi serial sau paralel.

Dacă locaţiile de

memorie pot fi accesate în orice ordine, iar timpul de acces este independent

de locaţia accesată, atunci accesul este aleator, iar unitatea de

memorie se numeşte memorie cu

acces aleator. În general, memoriile semiconductoare sunt memorii cu

acces aleator.

Prin ierarhizarea

unităţilor de memorie, blocurile de informaţii cu probabilitatea

cea mai mare de accesare sunt aduse pe niveluri superioare, mai aproape de

unitatea centrală (localitate spaţială). Dintre acestea,

informaţiile cele mai recent accesate sunt păstrate în apropierea

procesorului (localitate temporală).

Elementele subsistemului

ierarhizat de memorie, ilustrate în figura 1, sunt:

·

registrele procesorului (RP);

·

memoria cache (MC);

·

memoria primară sau principală (MP);

·

memoria intermediară (MI);

·

memoria secundară (MS);

·

memoria terţiară (MT).

Fig. 1. Elementele

subsistemului ierarhizat de memorie.

Registrele procesorului (RP) sunt cele mai rapide

elemente de memorare, dar şi cele mai scumpe. Acestea sunt accesate la

viteza internă a procesorului gazdă, viteză limitată de logica

de control a transferurilor dintre registre. Datorită tehnologiei actuale,

timpii de acces sunt foarte mici (zecimi de ns). Registrele au o capacitate de

memorare mică (sute de octeţi – KB) şi păstrează

informaţia primară (instrucţiuni şi date), necesară

procesorului în momentul prelucrării.

Memoria primară sau principală (MP) (primary memory, main

memory) reprezintă memoria de lucru a sistemului de calcul, fiind

realizată cu circuite integrate de memorie DRAM şi având o capacitate

de memorare relativ mare (sute de MB). MP păstrează informaţiile

active, care vor fi apelate de către procesor, dar care nu sunt imediat

necesare acestuia. Informaţiile devin active prin transferarea lor din MS

în MP, fiind memorate sub formă de blocuri de informaţii, în zone de

memorie, proprii fiecărui program. Viteza de lucru a MP este mult mai

mică decât cea a registrelor procesorului (cu 2–3 ordine de mărime),

având timpi de acces aleator de zeci până la sute de ns.

Memoria cache (MC), numită şi

memorie imediată, este o memorie de dimensiuni relativ mici (zeci – sute

de KB), mai rapidă decât memoria primară, care se interpune între

procesor şi MP, în scopul reducerii discrepanţelor mari dintre

performanţele acestora. Aceasta are rol de memorie tampon între procesor

şi MP, păstrând informaţiile cele mai recent folosite de

procesor, duplicări ale celor din MP . MC este o memorie rapidă,

realizată cu circuite integrate de memorie SRAM. Are timpul de acces de

2–10 ori mai mic (ns) decât cel

al memoriei primare, fiind însă şi de câteva ori mai scumpă. La

realizarea ei, se doreşte ca procesorul să lucreze cât mai mult timp

cu MC, şi nu cu MP. Pentru o memorie cache bine implementată,

procesorul lucrează cu aceasta circa 70–90 % din timpul total de lucru cu

memoria.

Memoria secundară (MS) este o memorie

nevolatilă şi reprezintă o extensie ieftină a MP, la fel

cum MP este o extensie ieftină a registrelor procesorului. În general, MS

este realizată cu unităţi de memorie pe suport magnetic (disc

magnetic, bandă magnetică) şi are capacităţi de

memorare foarte mari (zeci – sute de GB). Viteza de operare este mult mai

mică decât cea a MP, având un timp de acces cu 5–6 ordine de mărime

mai mare decât cel al MP. Fiind foarte lentă, MS este plasată în

subsistemul de intrare/ieşire şi este accesată prin intermediul

controlerelor. Principalul avantaj este costul unitar de memorare foarte mic.

Memoria intermediară (MI), numită şi

memorie cache pentru suporţi externi sau memorie cache de disc (Disk-Cached

Memory), este plasată între MP şi MS, acţionând într-o

manieră similară celei a MC. Are rol de memorie tampon, care

păstrează blocurile de informaţii cel mai recent accesate de un

program, duplicări ale celor din MS.

Memoria terţiară (MT), sau memoria de arhivare,

este o memorie nevolatilă de dimensiuni foarte mari, dar şi cu timpi

de acces foarte mari (zeci de secunde). Păstrează informaţii

pasive, stocate doar în scop de arhivare, accesul la acestea făcându-se

foarte rar. MT este realizată cu unităţi de memorare pe suport

detaşabil, optic (CD-ROM) sau magnetic (bandă sau casetă

magnetică). Trebuie subliniat faptul că MT reprezintă

colecţia de casete sau CD-uri existente, şi nu unităţile de

memorie propriu-zise.

2.2. Clasificarea memoriilor semiconductoare

Circuitele integrate de memorie (CIM)

sunt memorii semiconductoare, realizate în diverse tehnologii de

fabricaţie (bipolare sau MOS). Acestea sunt de mai multe tipuri, cu

diferite raporturi performanţe/cost, având domenii specifice de utilizare.

Dintre acestea, doar memoriile cu acces aleator (RAM) vor fi studiate în

continuare.

O

memorie cu acces aleator (RAM = Random Access Memory)

este acea memorie la care locaţiile de memorie pot fi accesate în orice

ordine, iar timpul de acces nu depinde de locaţia accesată.

Memoriile RAM pot fi de două

tipuri:

·

memorii SRAM (Static RAM), care memorează

informaţia în mod static;

·

memorii DRAM (Dynamic RAM), la care informaţia

este memorată în mod dinamic.

2.2.1. Memoria SRAM

Memoria SRAM (Static

RAM) este o memorie în care informaţia se memorează într-un mod

stabil, pe ambele niveluri logice, atât timp cât memoria este alimentată.

Este realizată în tehnologii rapide (bipolare sau CHMOS = Complementary

High-density MOS), cu timpi de acces foarte mici (câteva ns). Fiind o memorie care poate fi

şi citită şi scrisă, SRAM va avea magistrala

bidirecţională de date şi două cicluri diferite de memorie:

ciclul de citire şi ciclul de scriere, identificate de semnalul ![]() , activ pe 0L. Simbolul memoriei SRAM este ilustrat în figura

2.

, activ pe 0L. Simbolul memoriei SRAM este ilustrat în figura

2.

Fig. 2. Simbolul

memoriei SRAM

Memoria SRAM poate fi de

două tipuri:

·

Memoria SRAM

asincronă nu necesită semnal de ceas pentru sincronizarea cu unitatea master.

Memoriile asincrone sunt mai lente decât cele sincrone, dar sunt mai ieftine

şi au un consum de energie mic. Aceste memorii sunt realizate într-o

gamă foarte diversă de performanţe, cu timpi de acces ce

variază de la 50–70 ns, până la 10–15 ns.

·

Memoria SRAM

sincronă necesită un semnal de ceas pentru validarea semnalelor de control. Ceasul

primit din exterior permite operarea memoriei, sincron cu unitatea master.

Memoriile sincrone sunt foarte rapide, cu timp de acces sub 10 ns, pot

funcţiona la tensiuni de alimentare mici, dar sunt scumpe. Ele pot fi de

mai multe tipuri: PBS (Pipelined Burst Synchronous), FTS (Flow

Through Synchronous), ZBT (Zero Bus Turnaround) SRAM.

În general, sistemele de calcul

simple au memoria RAM de lucru formată doar din circuite de memorie SRAM

asincronă, cu capacităţi mici, de zeci-sute de KB, şi care

memorează cuvinte de 8 biţi. Sistemele performante, care

necesită viteze şi capacităţi de memorare mari, folosesc

memorii SRAM rapide pentru implementarea memoriei cache.

Din punct de vedere constructiv,

cele două tipuri de memorii SRAM sunt similare. Ele diferă doar prin

algoritmul de transfer al datelor şi implicit prin performanţe. De

aceea, în cele ce urmează vor fi analizate elementele comune, definitorii

pentru SRAM, iar exemplificările vor fi realizate pentru memoria asincronă.

Schema bloc a memoriei SRAM este

ilustrată în figura 3.

Fig. 3. Schema bloc a

memoriei SRAM.

2.2.2. Memoria DRAM

Memoria DRAM (Dynamic RAM)

este o memorie volatilă cu acces aleator, care memorează

informaţia în mod dinamic. Este realizată în tehnologie CMOS (Complementary

MOS), cu consum de energie foarte mic. Datorită

particularităţilor constructive ale celulelor de memorie,

informaţia 0L este memorată stabil, dar informaţia 1L se pierde

în timp şi necesită împrospătarea periodică a memoriei, de

unde şi denumirea acesteia.

Indiferent de modul de realizare,

memoria DRAM este mult mai lentă decât memoria SRAM, din cauza

mecanismului specific de memorare a informaţiilor. Timpul de acces la DRAM

este de 2–10 ori mai mare decât la SRAM, şi variază în funcţie

de tipul accesului la memorie.

Astfel, în acces aleator, timpul

de acces este mare (zeci de ns), însă scade foarte mult (în funcţie

de tipul memoriei DRAM), dacă se restricţionează accesul în mod

pagină, putând ajunge doar de două ori mai mare decât al memoriei

SRAM.

Celula de memorie este mult mai

mică decât la memoria SRAM, ceea ce permite realizarea unor

densităţi mari de integrare. Circuitele de memorie DRAM au, prin

urmare, capacităţi de memorare mari, şi implicit un număr

mare de linii de adresă. Simbolul memoriei DRAM este ilustrat în figura 4.

Fig. 4. Simbolul

memoriei DRAM.

Memorarea informaţiilor se

bazează pe stocarea şi transferul de sarcini electrice, şi nu pe

mecanisme de comutare, ca în cazul memoriilor SRAM. Fiecare bit de

informaţie este memorat prin încărcarea sau descărcarea unui

condensator. Când condensatorul este încărcat, se spune că se

memorează valoarea 1L, iar

când acesta este descărcat, valoarea memorată este 0L. Faţă de celula SRAM,

mecanismul de memorare nu presupune consum de curent de la sursa de alimentare.

Schema bloc de bază a

memoriei DRAM este trasată în figura 5.

Fig. 5. Schema bloc de

bază a memoriei DRAM.

Celulele

de memorie sunt dispuse într-o arie pătrată sau dreptunghiulară

de locaţii de memorie, fiecare locaţie memorând un cuvânt de m

biţi, Semnalele de comandă acţionează prin intermediul

logicii de control. Eventual, memoria DRAM poate avea circuit intern de

împrospătare, care presupune un numărător de adrese de rând

şi un ceas de timp real. În funcţie de tipul memoriei DRAM, ciclurile

de împrospătare pot fi realizate în trei moduri:

·

ROR (RAS

Only Refresh) este o metodă de împrospătare din exterior, prin care se

transmit memoriei adresa de rând (AR) şi semnalul![]() , fără a se activa semnalul

, fără a se activa semnalul![]() . Unitatea master externă este anunţată

periodic să facă refresh de către un ceas de timp real,

care este programat software de către sistemul de operare.

. Unitatea master externă este anunţată

periodic să facă refresh de către un ceas de timp real,

care este programat software de către sistemul de operare.

·

CBR (CAS

Before RAS) este tot o metodă de împrospătare din exterior, prin care se

transmit semnalele ![]() şi

şi ![]() , activate în această ordine. În acest caz, memoria

dispune de un numărător de adrese intern, pentru indicarea liniei

care trebuie împrospătată, fără a fi nevoie de transmiterea

adresei din exterior. De asemenea, perioada de repetiţie a ciclurilor de refresh

este determinată de un ceas de timp real extern.

, activate în această ordine. În acest caz, memoria

dispune de un numărător de adrese intern, pentru indicarea liniei

care trebuie împrospătată, fără a fi nevoie de transmiterea

adresei din exterior. De asemenea, perioada de repetiţie a ciclurilor de refresh

este determinată de un ceas de timp real extern.

·

Auto-împrospătare cu ajutorul circuitelor interne

memoriei DRAM. În interior, memoria conţine un numărător de

adrese de rând, un ceas de timp real şi o logică de control pentru

generarea semnalelor ![]() şi

şi ![]() , conform metodei CBR.

, conform metodei CBR.

Memoria DRAM poate fi de

două tipuri: asincronă şi sincronă.

Memoria DRAM asincronă nu

necesită semnal de ceas pentru sincronizarea cu unitatea master

apelantă. Ca şi la SRAM, memoriile DRAM asincrone sunt mai lente

decât cele sincrone, dar sunt mai ieftine şi au un consum de energie mai

mic.

Dintre memoriile DRAM asincrone,

se pot enumera: FPM (Fast Page Mode), EDO (Extended Data Out)

şi BEDO (Burst EDO) DRAM. La toate memoriile, accesul aleator este

lent. În acces aleator, timpul de acces faţă de RAS (tRAC)

este de 50–70 ns, iar timpul de ciclu (tC) este de 90–120 ns.

O altă categorie de memorii

DRAM este cea care utilizează o interfaţă sincronă. Prin

implementarea unei interfeţe sincrone, s-au eliminat perioadele de

aşteptare de către procesor, obţinându-se de asemenea unele avantaje

suplimentare. În cazul funcţionării sincrone, se memorează

anumite informaţii de la procesor în circuitele latch ale memoriei

DRAM sub controlul ceasului sistem. Aceste circuite păstrează

adresele, datele şi semnalele de control, ceea ce permite procesorului

să execute alte operaţii. După un număr specific de cicluri

de ceas, datele devin disponibile şi procesorul le poate citi de pe

liniile de ieşire.

Un alt avantaj al unei

interfeţe sincrone este că ceasul sistemului este singurul semnal de

sincronizare care trebuie furnizat memoriei DRAM. Aceasta elimină

necesitatea propagării semnalelor multiple de sincronizare. Intrările

sunt de asemenea simplificate, deoarece semnalele de control, adresele şi

datele pot fi memorate fără temporizările de setare şi

menţinere monitorizate de procesor. Avantaje similare se obţin

şi pentru operaţiile de ieşire.

O altă categorie este

reprezentată de memoriile DRAM bazate pe protocoale. Categoriile

precedente de memorii au linii separate de adrese, date şi control, care

limitează viteza la care poate funcţiona circuitul cu tehnologia

curentă. Pentru eliminarea acestui dezavantaj, au fost proiectate memorii

DRAM bazate pe protocoale, care implementează toate aceste semnale pe

aceeaşi magistrală. Cele mai cunoscute memorii din această categorie

sunt DRDRAM (Direct Rambus) şi SLDRAM (SyncLink) DRAM.

Memoria DRAM

sincronă necesită un semnal de ceas pentru validarea semnalelor de control.

Ceasul primit din exterior permite operarea memoriei, sincron cu unitatea

master. Deşi accesul aleator este comparativ cu cel al memoriilor

asincrone, accesul în mod pagină este mult mai rapid.

Memoriile sincrone pot fi de mai

multe tipuri: SDRAM (Synchronous DRAM), DDR SDRAM (Double Data Rate

SDRAM), RDRAM (Rambus DRAM), DRDRAM (Direct Rambus DRAM) etc.

Accesul

aleator este de asemenea lent, fiind puţin mai rapid decât la memoriile

asincrone, datorită tehnologiei (memoriile sincrone au apărut

ulterior). În acces aleator, tRAC

este de 40–60 ns, iar tC

este de 80–110 ns.

Accesul

în mod pagină este mult mai rapid decât la memoriile asincrone şi

depinde de frecvenţa semnalului de ceas de sincronizare.

2.3. Accesul la locaţiile

de memorie

În

sistemele bazate pe microprocesoare, modulele de memorie se conectează pe

magistrala sistemului. Accesul la locaţiile de memorie se realizează

prin cicluri de transfer (cicluri maşină), folosindu-se semnalele

magistralei (semnale de adresă, de date şi de comenzi). Modul de

desfăşurare a diferitelor tipuri de cicluri de transfer se

reprezintă prin diagrame de timp; diagrama prezentând evoluţia în timp

a semnalelor de pe magistrală implicate în transfer. Parametri de timp ai

unui ciclu de transfer depind de tipul procesorului, de regulile de

comunicaţie pe magistrala şi de tipul de circuite de memorie

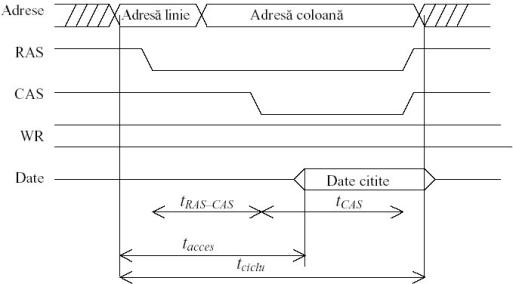

utilizate. În figura 6 s-au reprezentat diagramele de transfer pentru un ciclu

de citire din memorie şi un ciclu de scriere în memorie.

Fig. 6. Diagrame de citire/scriere memorie.

La

proiectarea unui modul de memorie trebuie să se ţină cont de

următorii parametri de timp:

·

timpul de acces la citire (tAR)

– intervalul de timp între momentul apariţiei adresei valide şi

momentul în care data citită este prezentă pe liniile de date; uneori

timpul de acces se măsoară în raport cu momentul de apariţie al

semnalului de comandă MEMR\; dacă timpul de acces al circuitului de

memorie folosit este mai mare decât timpul permis pe magistrală, atunci

interfaţa modulului de memorie trebuie să prelungească ciclul de

transfer prin dezactivarea pe un timp limitat a semnalului READY către

procesor.

·

timpul de menţinere a semnalului

de comandă MEMR\ activ (tMEMR).

·

durata unui ciclu complet de

citire sau scriere (tC).

·

timpul de

acces la scriere (tAW) – intervalul de timp între momentul în

care adresa este validă şi momentul de generare a comenzii de

scriere; în acelaşi mod ca la citire, dacă circuitul de memorie

folosit are un timp de acces mai mare, atunci interfaţa modulului trebuie

să dezactiveze temporar semnalul READY pentru prelungirea ciclului de

transfer; momentul activării semnalului de scriere se măsoară

şi în raport cu momentul în care data este prezentă pe

magistrală.

·

timpul de menţinere a

semnalului de scriere (tMEMW), de obicei < tMEMR.

Observaţii:

1.

la citire, data este

generată după apariţia semnalelor de adresă şi de

comandă şi se menţine un timp scurt după dezactivarea

acestora;

2.

la scriere, data trebuie

să apară pe magistrală înaintea semnalului de scriere şi

să fie validă pe toată durata de activare a semnalului de

comandă;

3.

timpul de acces acoperă

întârzierile care apar într-un modul de memorie datorită circuitelor de

decodificare a adresei şi de selecţie a amplificatoarelor de intrare

sau de ieşire

4.

proiectantul

trebuie să aleagă circuite de memorie cu parametri de timp

acoperitori pentru restricţiile impuse pe magistrală; trebuie să

se ia în calcul şi întârzierile produse de circuitele de amplificare din

interfaţă şi de pe magistrală.

2.4. Metodologia de proiectare

a memoriilor statice

Proiectarea

unui modul de memorie se face pe baza unor parametrilor de proiectare

impuşi:

·

capacitatea memoriei;

·

modul de organizare (unitatea

elementară de acces la memorie: octet, cuvânt, cuvânt dublu);

·

tipul de magistrală pe

care se conectează (numărul semnalelor de date şi de adrese,

tipurile semnalelor de comandă, parametrii de timp pentru ciclurile de

transfer);

·

amplasarea modulului de memorie

în spaţiul de adresare al procesorului, exprimată prin adresa sa de

început (trebuie să fie un multiplu al capacităţii modulului);

·

tipul de circuit de memorie

disponibil (poate fi un parametru impus sau unul ales de proiectant);

·

alte cerinţe speciale (de

exemplu: accesul dual de pe două magistrale, reîmprospătarea

controlată centralizat, implementarea unor mecanisme de detecţie a

erorilor etc.)

2.5. Metodologia de proiectare

a memoriilor dinamice

Proiectarea

memoriilor dinamice este în principiu similară proiectării memoriilor

statice, cu următoarele amendamente:

·

trebuie să se adauge un

mecanism de reîmprospătare periodică a memoriei (refresh);

·

adresele trebuie multiplexate

(generarea secvenţială pe aceleaşi semnale a adresei de linie

şi a adresei de coloană);

·

trebuie să se genereze

semnalul de validare a adresei de linie (RAS – Row Address Select)

şi semnalul de validare a adresei de coloană (CAS – Column Address

Select);

·

selecţia circuitelor se

face cu semnalele RAS şi CAS (excepţie fac circuitele de tip

EDO-DRAM, care au semnal separat pentru selecţia circuitului).

Pentru circuitele RAM dinamice, multiplexarea în timp a

adreselor a fost necesară pentru a reduce numărul de pini ai

circuitului de memorie şi, implicit, dimensiunea acestuia. De notat

că circuitele dinamice au o capacitate relativ mare, ceea ce impune un

număr mare de linii de adresă pentru selecţie. Organizarea

internă a unei memorii dinamice este sub forma unei matrice, cu linii

şi coloane; selecţia unei locaţii se face prin specificarea

adresei sale de linie şi de coloană.

Reîmprospătarea periodică a memoriei este

necesară deoarece informaţia este păstrată un timp limitat

după ultima operaţie de citire sau scriere (condensatorul care stochează

informaţia se descarcă în timp).

Controlul

procesului de reîmprospătare poate să se facă la nivelul

modulului de memorie sau centralizat la nivelul întregului sistem. Indiferent

de metoda aleasă, proiectantul trebuie să se asigure că

ciclurile de reîmprospătare nu se suprapun peste ciclurile obişnuite

de citire sau scriere. Reîmprospătarea se face simultan la nivelul unei

linii întregi din matricea de memorie.

În

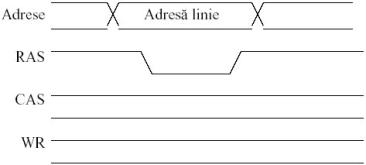

figurile 7, 8 şi 9 s-au reprezentat diagramele de timp pentru ciclurile de

citire din memorie, scriere în memorie şi, respectiv, reîmprospătare

a memoriei.

Fig. 7. Ciclu de citire din memorie.

Fig. 8. Ciclu de scriere în memorie.

Fig. 9. Ciclu de reîmprospătare a memoriei.

3. Descrierea aplicaţiei

Aplicaţia

SRAMvsDRAM este formată din 6 ferestre.

3.1. Meniul principal

Fereastra meniului principal (vezi figura 10)

conţine două butoane de comandă (Memoria SRAM şi Memoria

DRAM), iar prin apăsarea acestora se deschide dialogul

corespunzător opţiunii făcute. Fereastra deschisă prin

apăsarea oricărui buton declanşează un eveniment şi

astfel este permisă deschiderea mai multor submeniuri în acelaşi

timp. Revenirea la meniul principal se poate face după închiderea submeniului

apelat sau prin deplasarea focusului pe fereastra principală.

Fig.

10. Meniul principal al aplicaţiei.

Din punctul de vedere al utilizatorului, parcurgerea

meniului este foarte simplă: el trebuie să selecteze una dintre cele

două opţiuni disponibile în cadrul meniului.

3.2. Memoria RAM statică

Apăsarea butonului Memoria RAM statică

din meniul principal va deschide o nouă fereastră (vezi figura 11),

în care utilizatorul poate opta pentru:

·

butonul Operaţii de

citire/scriere ale memoriei SRAM;

·

un exerciţiu de

dimensionare hardware, în care utilizatorul poate calcula numărul de

tranzistori necesar unei anumite capacităţi de memorare.

S-au

folosit două combobox-uri şi două grupuri a câte

două butoane radio, prin care utilizatorul poate selecta capacitatea

memoriei, cu valori cuprinse între 16 şi 2048, multiplul valorii

capacităţii, care poate avea două valori: K (Kilo) şi M

(Mega), unitatea de mărime, de asemenea cu două valori posibile: b

(bit) sau B (Byte sau octet), precum şi numărul de tranzistori pe

celulă de memorie, cu valori cuprinse între 3 şi 10. Fereastra mai

cuprinde un textbox în care se face afişarea numărului de

tranzistori, după apăsarea butonului calculează.

3.3. Operaţii de citire/scriere

ale memoriei SRAM

Această fereastră este formată din

două combobox-uri care folosesc la alegerea timpilor de acces la

memorie şi de ciclu, ambii parametrii având gamele de valori prestabilite.

Fig.

11. Memoria RAM statică.

Fig.

12. Operaţii de citire/scriere ale memoriei

SRAM.

Fereastra

mai cuprinde un textbox care atenţionează utilizatorul în

cazul în care acesta a acţionat unul dintre cele trei butoane existente

fără să fi selectat în prealabil valori pentru aceşti

timpi.

Pe baza

celor două valori alese, prin apăsarea butoanelor existente în

fereastră, se vor construi diagramele de timp pentru (vezi figura 12):

·

ciclul de citire din memoria

SRAM asincronă;

·

ciclul de scriere în memoria

SRAM asincronă;

·

ciclul de scriere în memoria

SRAM fără semnalul ![]() .

.

Diagramele

rezultate sunt formate din semnale de adresă şi semnale de

comandă (de validare a circuitului de memorie ![]() , a ieşirilor memoriei

, a ieşirilor memoriei ![]() şi de validare a ciclului de scriere

şi de validare a ciclului de scriere ![]() ). Locaţiile de memorie

sunt accesate prin intermediul adreselor trimise pe magistrala de adrese (ADR).

). Locaţiile de memorie

sunt accesate prin intermediul adreselor trimise pe magistrala de adrese (ADR).

La memoriile asincrone, o nouă operaţie poate

începe după încheierea timpului de ciclu. În acest caz, se observă

că magistrala de date este ocupată mai mult timp decât în cazul

anterior. De asemenea, semnalul ![]() nu trebuie activat după

semnalul

nu trebuie activat după

semnalul ![]() , deoarece s-ar activa circuitul de ieşire din SRAM în

timpul scrierii.

, deoarece s-ar activa circuitul de ieşire din SRAM în

timpul scrierii.

3.4.

Memoria RAM dinamică

Această

fereastră cuprinde următoarele butoane, care conduc la deschiderea

altor două ferestre (vezi figura 13):

Fig.

13. Memoria RAM dinamică.

·

Operaţii de

citire/scriere/împrospătare ale memoriei DRAM,

pentru trecerea la fereastra diagramelor de semnale;

·

Înainte,

pentru trecerea la fereastra dedicată parametrilor memoriei DRAM.

În

fereastra Memoria RAM dinamică se pot calcula următorii

parametri:

·

perioada de repetiţie a

ciclurilor de refresh (în μs), în funcţie de timpul de

reîmprospătare (în ms) şi numărul de linii al unei arii dreptunghiulare

de memorie;

·

gradul de ocupare a memoriei cu

împrospătarea (în %), care se poate calcula în funcţie de durata

ciclurilor de împrospătare (în ms) şi perioada de repetiţie a

ciclurilor de împrospătare (în μs);

·

rata de transfer a memoriei

DRAM (în MB/s), în funcţie de lăţimea magistralei de date

şi frecvenţa semnalului de ceas (în MHz).

Pentru alegerea parametrilor s-au folosit combobox-uri

cu valori prestabilite, iar pentru afişarea rezultatelor s-au folosit textbox-uri

validate prin apăsarea butoanelor calculează.

În cadrul procedurii de

încărcare a ferestrei, se iniţializează variabilele din fiecare

segment în parte. Astfel, din punctul de vedere al utilizatorului,

apăsarea unui buton de comandă declanşează procesul de

calcul şi returnează un rezultat într-o anumită unitate de

măsură, în funcţie de segment.

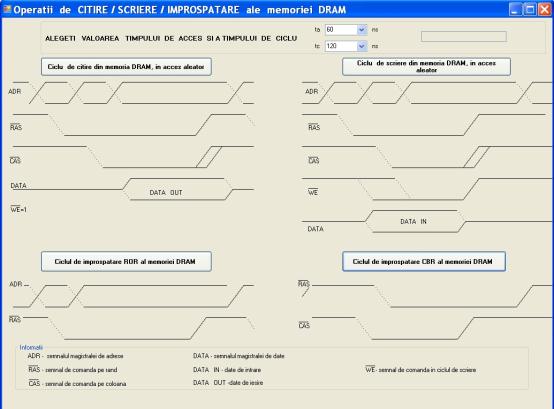

3.5. Operaţii de

citire/scriere/împrospătare ale memoriei DRAM

Această

fereastră prezintă diagramele de timp ale ciclurilor de citire,

scriere şi împrospătare (vezi figura 14).

Fig.

14. Operaţii de

citire/scriere/împrospătare ale memoriei DRAM.

Acestea se

construiesc pe baza variabilelor de intrare: timpii de acces la memorie şi

de ciclu, ambii parametri având gamele de valori prestabilite. Diagramele de

timp trasate sunt descrise de semnalele de comandă şi de

conţinutul magistralelor de adrese şi de date.

Pentru

ca memorarea adreselor să fie corectă, adresele de rând şi de

coloană trebuie să fie stabile un interval de timp înainte şi

după momentul activării semnalelor de comandă

corespunzătoare, ![]() şi

şi ![]() . După activare,

semnalele de comandă

. După activare,

semnalele de comandă ![]() şi

şi ![]() trebuie să

rămână active până la sfârşitul ciclului, deoarece, prin

logica de control, acestea au rolul de validare a circuitului de memorie

şi a ieşirilor. Funcţia de trasare a diagramelor de timp se

declanşează prin apăsarea butoanelor corespunzătoare.

trebuie să

rămână active până la sfârşitul ciclului, deoarece, prin

logica de control, acestea au rolul de validare a circuitului de memorie

şi a ieşirilor. Funcţia de trasare a diagramelor de timp se

declanşează prin apăsarea butoanelor corespunzătoare.

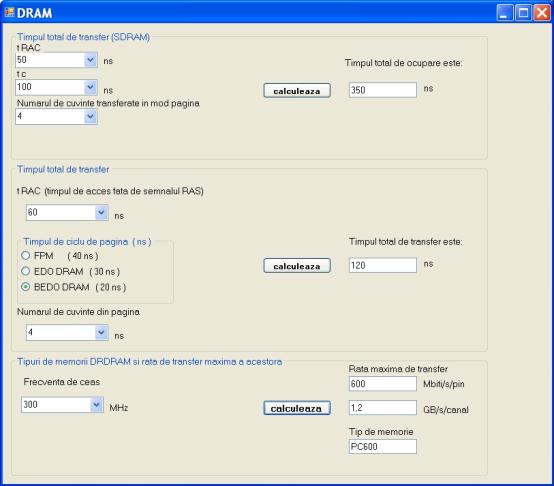

3.6. Parametrii memoriei

DRAM

Ultima

fereastră a aplicaţiei oferă utilizatorului posibilitatea de

calculare a următorilor parametri (vezi figura 15):

·

timpul

total de ocupare al memoriei (în ns);

·

timpul

total de transfer (în ns);

·

rata

maximă de transfer pentru diferite tipuri de memorii (în Mb/s/pin sau

GB/s/canal).

Fig.

15. Parametrii memoriei DRAM.

Calculul se face pe baza variabilelor de intrare, selectate prin combobox-uri şi butoane radio din seturi de valori predefinite. Aceste variabile de intrare sunt:

·

timpul de acces faţă de

RAS tRAC , timpul de ciclu tC (ambii în

ns), numărul de cuvinte transferate în mod pagină – pentru

calculul timpului total de ocupare;

·

timpul de acces faţă de

RAS tRAC, timpul de ciclu în pagină (ambele în ns)

şi numărul de cuvinte din pagină – pentru calculul timpului

total de transfer;

·

frecvenţa de ceas (în MHz)

şi tipul de memorie – pentru calculul ratei maxime de transfer.

Fereastra

mai cuprinde şi 4 textbox-uri, în care se face afişarea

parametrilor, după apăsarea butoanelor calculează.

4. Desfăşurarea

lucrării

1.

Se studiază partea teoretică a lucrării.

2.

Se lansează aplicaţia SRAMvsDRAM.exe.

3.

Se selectează opţiunea Memoria RAM

statică.

3.1. Se presupune că se

doreşte realizarea unei memorii cache de nivel 2, integrată în

microprocesor, cu capacitatea de memorare de 512 KB. Dacă celulele de memorie au câte 6 tranzistori,

atunci să se determine numărul total de tranzistori necesari pentru

MC.

3.2. Se reiau

determinările pentru alte seturi de date de intrare şi se

notează rezultatele obţinute.

4.

Se selectează opţiunea Operaţii de citire/scriere ale memoriei

SRAM.

4.1. Se alege un set de valori

pentru timpul de ciclu şi timpul de acces.

4.2. Se vizualizează

şi se desenează diagramele de timp pentru ciclurile de citire şi

scriere.

4.3. Se reiau

reprezentările pentru alte seturi de date de intrare şi se reţin

rezultatele obţinute.

5.

Se selectează butonul Memoria RAM dinamică

şi se studiază cazurile următoare din cadrul meniului şi

submeniurilor ferestrei:

5.1. Un circuit de memorie DRAM are capacitatea de memorare de 64 Kb.

Celulele de memorie trebuie împrospătate după un timp de maximum 2 ns şi sunt organizate într-o

arie dreptunghiulară, cu 128 linii şi 512 coloane. Să se

calculeze perioada de repetiţie a ciclurilor de refresh. Se reiau

determinările pentru alte seturi de date de intrare şi se

notează rezultatele obţinute. Se notează rezultatele

obţinute.

5.2. Cunoscând durata ciclurilor de împrospătare şi perioada de

repetiţie a acestora, se va determina gradul de ocupare a memoriei cu

împrospătarea, ca procent din timpul total de lucru al memoriei. De

exemplu, pentru memoria DRAM din exemplul anterior, se cunoaşte durata

ciclurilor de împrospătare (250 ns). Să se calculeze gradul de

ocupare a memoriei cu împrospătarea. Se reiau determinările pentru

alte seturi de date de intrare şi se notează rezultatele

obţinute.

5.3. Să se calculeze banda maximă susţinută de transfer

pentru o memorie DDR-SDRAM, la frecvenţa semnalului de ceas de 400 MHz

(folosind aplicaţia) şi 600 MHz (exerciţiu de calcul). Se

notează rezultatele obţinute.

5.4. Se vizualizează şi se

desenează diagramele de timp pentru ciclurile de citire, scriere şi

reîmprospătare în cazul mai multor seturi de valori ale timpului de acces

şi timpului de ciclu.

5.5. Se repetă calculul de la punctul 5.3 pentru o memorie RDRAM. Se

notează rezultatele obţinute.

5.6. Se presupune că cele trei tipuri de

memorii DRAM asincrone (FPM, EDO RAM şi BEDO DRAM) au timpul de acces

faţă de RAS tRAC = 70 ns şi timpul de ciclu tC

= 120 ns. Dacă memoriile sunt accesate aleator, transferându-se câte un

singur cuvânt, atunci accesul durează 70 ns, dar următorul acces nu

poate fi început decât după timpul de ciclu de 120 ns. De aceea, la citirea mai

multor cuvinte (de exemplu, la citirea a 4 cuvinte), primul cuvânt este citit

după 70 ns, dar următoarele citiri durează câte 120 ns, deci,

timpul total se calculează astfel: tRAC

+ (n–1)tC, unde n

este numărul de cuvinte citite. Să se calculeze timpul total de

ocupare şi timpul total de transfer. Se notează rezultatele

obţinute.

5.7. Se consideră aceleaşi memorii DRAM, cu tRAC = 70 ns şi tC = 120 ns. Dacă se

iniţiază un acces în mod pagină, de exemplu pentru citirea a 4

cuvinte din pagină, atunci primul acces durează tRAC

= 70 ns, însă următoarele 3 cuvinte sunt accesate cu timpul de ciclu

de pagină (tPC), mai rapid, în funcţie de tipul

memoriei, conform expresiei modificate: tRAC

+ (n–1)tPC, unde n

este numărul de cuvinte citite. Să se calculeze timpul total de

transfer pentru FPM, BEDO RAM şi EDO DRAM. Se notează rezultatele

obţinute.

5.8. Să se calculeze rata maximă de transfer a unei memorii de

tip PC600/800, pentru o frecvenţă de ceas de 300, respectiv, 400 MHz.

Se notează rezultatele obţinute.

5. Întrebări

1.

Definiţi şi caracterizaţi memoria SRAM.

2.

Discutaţi, comparativ, cele două tipuri de

memorii SRAM. Care sunt domeniile lor de aplicabilitate?

3.

Explicaţi semnificaţia semnalelor de

comandă ale memoriei SRAM.

4.

Utilizând schema bloc a memoriei SRAM, să se descrie

modul de selectare a unei celule de memorie.

5.

Descrieţi funcţionarea

logicii de comandă a circuitului I/O al memoriei SRAM.

6.

Cum se modifică logica de comandă la memoriile

fără semnalul OE?

7.

Explicaţi modul de execuţie al ciclului de

citire din memoria SRAM.

8.

Discutaţi, comparativ, cele două diagrame ale

ciclului de scriere, corespunzătoare memoriilor SRAM, cu şi

fără semnalul OE.

9.

Explicaţi care sunt modurile de realizare a

împrospătării conţinutului memoriilor DRAM.

10. Analizaţi comparativ

memoriile DRAM sincrone şi asincrone.

11. Cum acţionează

semnalele RAS şi CAS pentru împrospătarea memoriei?

12. Să de

definească parametrii de timp de care trebuie să se ţină

seama la proiectarea unei memorii şi să se explice relaţiile de

condiţionare între aceste valori.

13. Comparaţi

metodologiile de proiectare pentru memoriile statice şi dinamice.

14. Ştiind că

microprocesorul Pentium III are 9 milioane de tranzistori, să se explice

cum poate fi integrată în microprocesor o memorie cache de nivelul 2, care

necesită 25 milioane de tranzistori.

15. Caracterizaţi

memoria DRAM şi explicaţi diferenţele faţă de memoria

SRAM care apar la conectarea cu exteriorul.

16. Cum intervine semnalul de

comandă WE în modul de transfer al memoriilor dinamice, comparativ cu cele

statice?

17. Ordonaţi

tipurile de memorii descrise în lucrare după criteriul vitezei de lucru.